## Peta Hertz Clock based Peta bits per Second Speed PRBS- GPS HDL Transceiver Design for Ultra High Speed GPS Mobile Phone Computing System

Prof P.N.V.M SASTRY1

Dean- Engineering-IT EDA Software Industry CELL & R&D CELL & ECE Joginpally B.R. Engineering College Hyderabad -75, India

### Prof Dr.D.N.Rao2

Principal

Joginpally B.R Engineering College Hyderabad -75, India

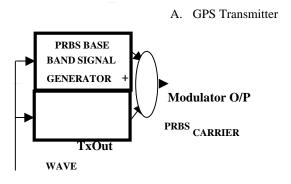

Abstract-The Aim is for HDL Design & Implementation of PRBSBased GPS SOC Transceiver Design using VHDL & VerilogHDL. GPS SOC Transceiver contains Transmitter & Receiver and

Transceiver SOC by Integration of Transmitter & Receiver. Transmitter Contains PRBS – Base Band Signal Navigation Data Generator with frequency of 50 Hz & Carrier Wave Generator with a frequency of 1.057 MHz and C(t) is Pseudo Random Code (C/A Code of Satellite is 1.023 MHz). PRBS GPS Base Band

Signal Generator & Carrier Wave Generator are XORed by using XOR Gate for generation of Digital Modulated Signal by Tapping Different Sequence Patterns 2e7-1,2e10-1,2e15-1,2e23-1,2e31-1 etc as per CCITT – ITU Standards (O.150,O.151,O.1<del>52) for</del> Identification of Property of PRBS Modulated Signal codes and the same signal codes received by using PRBS <u>GPS</u> Receiver System and compared with the Received sign<del>al</del> codes delayed with Transmitted one, and if the result is '0', no error in the received

sequence. '1' means error occurred in the received sequence. Speed of Transmission rate is in terms of Peta Bits Per Second Coding done by VHDL &/ Verilog HDL. Programming & Debugging Done by Xilinx ISE <u>9.2i</u> Software Design Tool and Xilinx Spartan III FPGA Development Kit.

**Keywords-**C/A – Coarse Acquisition , GPS –Global Position System , VHDL – Very High Speed Integrated Circuit Hardware Description Langunge, FPGA – Field Programmable Gate Array. SOC – System On Chip.

### 1. INTRODUCTION

In Modern Hi-tech Wireless GPS Mobile Computing Systems & Communication Engineering Applications and Products, GPS Played Prominent Role for Acquisition and Tracking of Data like Longitude and Latitude of the Satellites in space, for Acquisition and Tracking of Position Of Objects like Line Sight in Space- Troposphere, IonoSphere Layers, Detection of Objects like Location & Position of The Objects on the Earth and Space by using Google Map Software Site interface with GPS Mobile Computing System through wireless system connectivity.

The Detection Of Objects on Earth like Cars, Vehicles on the road, Navy objects-Fleet Management Systems, Geo Stationery Satellites etc. Similarly The Detection Of Objects

on Space like Acquisition and Tracking of Location and Position Of Satellites, Flights/Air-Crafts, Space Vehicles.

GPS SOC Transceivers Mainly used for this purpose. The Rate Transmission and Reception of Data Speed is in terms of Peta <u>Bits</u> Per Second because GPS Mainly used Two Carrier Wave Frequency Ranges – Civilian and Military

Frequency Standards. These are L1 (1575.42 MHz) and L2 (1227 MHz). L1 is primarily a Civilian signal while L2 is used for Military purposes. Now I Designed Peta Bits Per Second Clock Speed Rate PRBS Based GPS SOC

Transceiver for Acquisition and Tracking of Large Complex

Data (Cloud Computing / Wireless Internet Computing Data

) based Position and Location Objects like Maps, Images, Graphics Animated Data, Security Data etc. Now a Days w.r.t Peta Hertz Clock Speed, the rate of speed of transmission and reception is in terms of Multiple Data Packets /bytes / Frames/words/super words. The Total Objects location and position finding in terms of Longitude and Latitude frames. For Higher Bandwidth rate of Frequency and Network Cloud Purpose, Various Spread

Spectrum and Shift keying techniques are used, these are

Direct Sequence Spread Spectrum, Frequency Hopping, Chaotic Spread Spectrum, LDPC Techniques and shift keying Techniques like BPSK, DPSK, and QPSK etc. It is almost similar like CDMA Communication Systems. Now a Days All GPS Products are So Hi-tech Portable Computing

Systems Because Of VLSI Design Technology in terms 90,

60, 10 nano meters Geometric Dimension Size of the Chips

- according to Micron and Lambda based Chip Design

Rules. Current Trend of GPS SOC Transceivers Designed

In terms of Nano Meters Size. Now I Designed Universal GPS SOC Transceivers with 100 nano meter Micron Size.

Due to this Single Chip Solution, Portable Hi-tech GPS Mobile Satellite Hand Held Instruments / Computing Systems Came to the Market for wide range applications usage, Now a Days a Common Man using GPS in Multimedia Mobile Phones, Card less Mobile Phones,

Tablets, Mobile Phones, I-Phones, eepads, Note Book

Computers, Pocket Mobile Multi Media Computing

Systems for finding the Detection of Long Distance Objects, Line of Sight, Latitude, Longitude position and location with the help software sites like Google Map etc and the PRBS GPS SOC Transceivers are So Popular and Wide Range of Applications like Wireless and Telecom,

Consumer, Medical Diagnostics, Satellite & Space

Applications, Military, Radar, Civilian, Defense, Security

Figure 1.PRN Code

System Applications, Cloud & cluster, Internet Computing Software Systems, Aerospace/Avionics. PRBS GPS SOC

ASIC Core mainly suit for finding the Locations and Positions of Long Distance Communication Objects through LTE ASIC IP Core Protocol s and Switches. All Latest Mobiles and Tablets Manufacturers like Intel,

Samsung, Apple, Google, HTC, Lucent(Formerly AT &T (American Telegraph and Telephone) Bell Labs, Sony. All these manufactured based Mobile Phones having GPS Facility.

A. Object Detection using PRN Code

GPS Satellites uses Spread Spectrum Techniques for Spreading the unique Code words of Base Band Signal Data with the help Carrier Frequency Standards The GPS Satellites transmit navigation signals on two carrier frequencies called L1, the primary frequency, and L2, the secondary frequency. The carrier frequencies are DSSS modulated by spread spectrum codes with unique PRN (Pseudo Random Noise) sequences associated with each SV and by a common navigation data message. Each GPS satellite broadcasts two types of PRN ranging codes: a short

Coarse / Acquisition (C/A)-code and a long precision (P)-code. The C/A code has a 1-ms period and repeats constantly, whereas the P-code satellite transmission is—a 7-day sequence that repeats approximately every Saturday/Sunday midnight

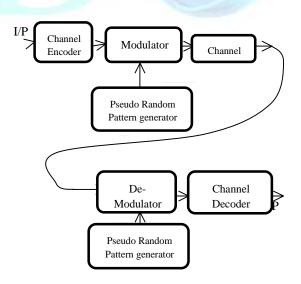

Figure 2. Digital Spread Spectrum System

## II. PRBS GPS SOC TRANSCEIVER DESIGN ARCHITECTURES

### Peta Hertz Clock

### Peta Hertz Clock

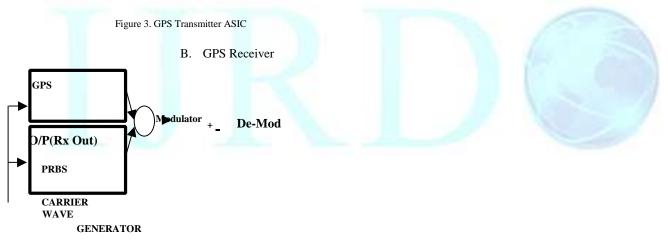

Figure 4. GPS Receiver ASIC

Figure 11. Peta PRBS GPS Transmitter

### B.GPS RECEIVER RTL LOGIC BLOCK

Figure 12. Peta PRBS GPS Receiver C. Peta PRBS GPS Checker RTL LOGIC BLOCK

Figure 13. Peta PRBS GPS Checker RTL

D. GPS Transmitter FPGA Placed Design Report

G.GPS Transmitter FPGA Routed Layout Design Report Figure 14. Peta Hertz PRBS GPS Tx

|                   |     |     | ALL LA |

|-------------------|-----|-----|--------|

| ÷ (1              | 154 | e g |        |

| COLUMN TWO IS NOT |     |     | <br>   |

#### Figure 17. GPS Transmitter Routed Report

V. REFERENCES

- [1] Wikipedia , http://en.wikipedia.org/wiki/ Pseudorandom\_binary\_sequence

- [2] "ITU-T Recommendations O151, O152 and O153," Tech. Rep.

- [3] Xilinx Data Sheet

- [4] <u>http://en.wikipedia.org/wiki/Linear\_feedback\_shift\_regist</u> er

[5] SY Hwang, GY Park, DH Kim, KS Jhang, "Efficient Implementation of a Pseudorandom Sequence Generator for HighSpeed Data Communications", ETRI Journal, Volume 32, Number 2, April 2010.

E. GPS Receiver Placed Design Report

Figure 15.Peta Hertz PRBS GPS Rx

F.GP<u>S</u> Receiver Routed Report

Figure 16.Peta Hertz PRBS Receiver Routed Report

VI. Conclusion

This is Mainly Designed for High

Speed

Transmission & Reception of GPS Data in terms of Peta

Bits Per Second Speed Rate for Acquisition & Tracking of

Data through Transmitter & Receiver at Peta Hertz Clock Frequency Rate . This is very High Speed Transceiver in the latest current technology trends and suit for all latest real time VLSI & Embedded Smart Computing Consumer & Wireless Computing Products & Applications. This Design has very Less Complexity in Size & Compatible compared to other GPS Transceivers.

#### VII.Author Profile

Prof P.N.V.M Sastry Currently working with a Capacity of Dean- IT EDA Software – R&D CELL & ECE DEPARTMENT, He Did Master Degree In

Science- M.S Electronics, Under Department Of Sciences, College Of Science & Technology AU - 1998.Did PG Diploma In VLSI Design From V3 Logic Pvt Ltd B'Lore-2001, Did M.Tech (ECE) From IASE Deemed

University-2005. Currently Pursuing (PhD)-ECE(VLSI), JNTU Hyderabad -2012, Over Past 16 years of Rich Professional Experience with Reputed IT Software Industrial MNC's, Corporate –CYIENT (INFOTECH) (World top CMMi Maturity Level 5 Version 1.2

Confirmed Very few listed Global IT Software Engineering Services

MNC), ISiTECH as a world top keen IT Industrial Software Specialist

- World Top Software Engineering Team Leader(Level 6) Eng-Eng-

#### HCM Electronics Vertical & Program Manager - MFG

I/C,EDS,BT,NON BT Embedded Software ,Avionics & Automotive Hitech Software Engineering Verticals & Departments , Program Lead – Embedded & VLSI & Engineering Delivery Manager – IT Semiconductor Software Engineering Vertical ,at ISiTECH , also worked with Govt R&D, Industrial Organizations, Academic Institutions of Comparative Designations & Rolls . His Areas Of Interest are VLSI – VHDL, Verilog HDL, ASIC, FPGA & Embedded Software Product Architectures Design & Coding Development .He mentored & Architecting Various Real Time, R&D, Industrial Projects/Products related to VLSI & Embedded System Software & Hardware.. His Key

Achievements are Participated Various Top Class International IT MNC Delegates Board Meetings, IT Software MNC Board Meetings(Tier1/2 Level MRM-VP,COO Level) , Guided R&D ,Industrial , Academic Projects /Products –VLSI-ASIC,FPGA & Embedded & Embedded,VLSI Software Project &/ Program Management & Also Coordinated Various In House & External IT Project Workshops & Trainings At CYIENT( INFOTECH) as a I/C- MFG Eng Software Vertical , Also Participated Various National R&D Workshops, FESTS, FDP's & Seminars. Recently He Published Various national & International Journals, Conferences.

**Dr. D.N Rao B.Tech,M.E,Ph.D, principal** of JBREC, Hyderabad. His carrier spans nearly three decades in the field of teaching, administration,R&D, and other diversified in-depth experience in academics and administration. He has actively

involved in organizing various conferences and workshops. He has published over 11 international journal papers out of his research work. He presented more than 15 research papers at various national and international conferences. He is Currently approved reviewer of IASTED International journals and

conferences from the year 2006. He is also guiding the projects of PG/Ph.D students of various universities